سامسونگ تولید انبوه تراشههای مبتنیبر لیتوگرافی 3 نانومتری را از هفته آینده آغاز میکند

براساس گزارش Yonhap News، انتظار میرود سامسونگ تولید انبوه تراشههای 3 نانومتری را هفتهی آینده آغاز کند. درحالیکه، TSMC رقیب سامسونگ، تولید تراشههای 3 نانومتری را از نیمهی دوم سال جاری شروع خواهد کرد و بدینترتیب، غول کرهجنوبی در این زمینه از رقیب تایوانی خود سبقت خواهد گرفت.

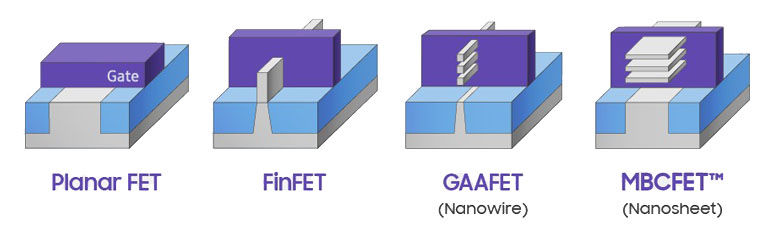

طبق گزارش جیاسامآرنا، لیتوگرافی 3 نانومتری سامسونگ در مقایسه با فرایند 5 نانومتری این شرکت که در تولید تراشههای اسنپدراگون 888 و اگزینوس 2100 از آن استفاده شده است، 35 درصد مساحت کمتر و 30 درصد عملکرد بهتر و 50 درصد مصرف انرژی بهینهتری خواهد داشت. دستیابی به این آمار بهلطف بهرهمندی از طراحی موسوم به Gate-All-Around (GAA) در ترانزیستورها بهدست آمده است. درحقیقت، این تکنولوژی گام بعدی پس از FinFET است؛ زیرا به شرکتهای تراشهسازی اجازه میدهد بدون کاهش توانایی ترانزیستورها در انتقال جریان آنها را کوچک کنند. طراحی GAAFET استفاده شده در لیتوگرافی 3 نانومتری در تصویر زیر نمایش داده شده است.

رئیس جمهور ایالات متحده، جو بایدن، ماه گذشته از کارخانهی سامسونگ در پیونگتاک بازدید کرد تا در مراسم نمایش فناوری 3 نانومتری این کمپانی حضور یابد. سال گذشته، صحبتهایی مبنیبر این موضوع مطرح شد که این شرکت میتواند 10 میلیارد دلار برای ساخت کارخانهی ریختهگری 3 نانومتری در تگزاس سرمایهگذاری کند. درحالحاضر این سرمایهگذاری به 17 میلیارد دلار افزایش یافته است و انتظار میرود کارخانهی مورد اشاره سال 2024 شروع به کار کند.

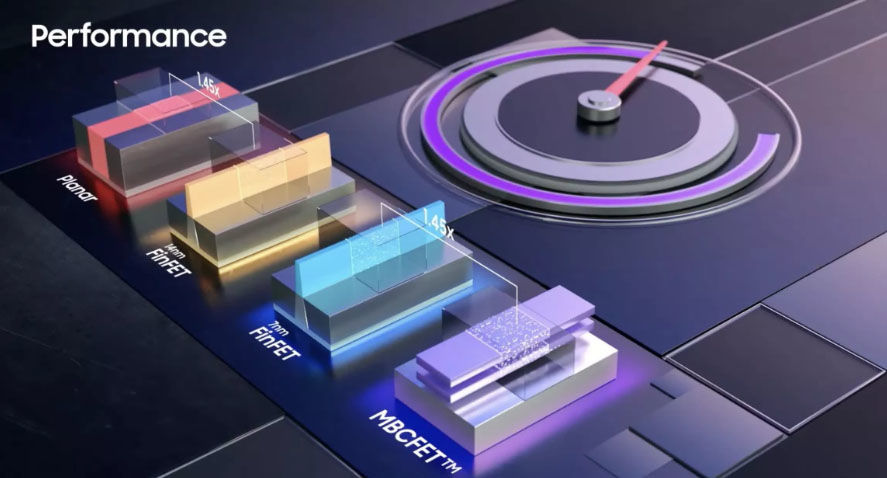

بههرحال، اکنون بزرگترین نگرانی به بازدهی لیتوگرافی جدید سامسونگ مربوط میشود. شرکت مذکور در اکتبر سال گذشته اعلاکم کرد که بازده فرایند 3 نانومتریاش به سطحی مشابه با فرایند 4 نانومتری نزدیک خواهد شد. اگرچه این شرکت در این زمینه هرگز آمار رسمی ارائه نداده است، تحلیلگران اعتقاد دارند لیتوگرافی 4 نانومتری غول کرهجنوبی با مشکلاتی بازدهی مواجه بوده است. نسل دوم لیتوگرافی 3 نانومتری در سال 2023 از راه خواهد رسید و نقشهی راه سامسونگ نیز شامل فرایند 2 نانومتری مبتنیبر MBCFET در سال 2025 است.